# PCN 11773 – Additional information MIM module process change in Samsung Foundry: MIM HAH stack implementation on 32LP, 28LP and 28FD Technologies

## WHAT is the change?

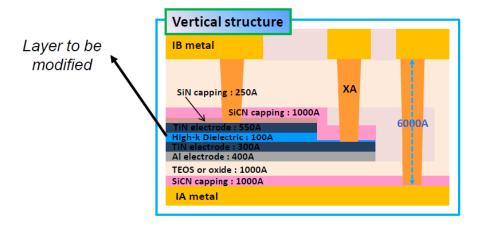

Metal Insulator Metal (MIM) capacitance insulator (dielectric) change from Ta2O5 material to HfO2/AI2O3/HfO2 (HAH) tri-layer for performance and throughput/capacity improvement

| Layers (for MIM)                | Parameters | Thick | Thick Var | ĸ   |

|---------------------------------|------------|-------|-----------|-----|

| Units                           | Units      | [A]   | [A]       |     |

| Above MIM top plate (conformal) | Nitride    | 600   | 60        | 8.1 |

| MIM top plate                   | TiN        | 550   | 55        |     |

| Dielectric between MIM plates   | MIM diel   | 115   | 11        | 25  |

| MIM bottom plate                | TiN        | 300   | 45        |     |

| MIM bottom plate                | AI         | 400   | 40        |     |

| Below MIM bottom plate          | Oxide      | 1000  | 100       | 4.2 |

| Process items                               | Current process                      | Current tool | New process                                                                           | New tool |

|---------------------------------------------|--------------------------------------|--------------|---------------------------------------------------------------------------------------|----------|

| MIM Insulator<br>(dielectric)<br>Deposition | Ta <sub>2</sub> O <sub>5</sub> layer | Emeral3000   | HfO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub><br>(HAH) tri-layer | Pulsar   |

Samsung Foundry decided to qualify a new equipment on Line 32LP, 28LP and 28FD for performance and throughput/capacity improvement:

- Ta2O5(TAO) deposition tool out of production (only 3 chambers worldwide)

- Complex PM and parts delivery time higher for TAO

- Higher support on HAH stack, because used on advanced technology nodes (14/10nm)

|                 | TAO<br>(POR)                                  | HAH<br>(SF Proposal)                        |  |

|-----------------|-----------------------------------------------|---------------------------------------------|--|

| Model           | Emeral 3000                                   | Pulsar                                      |  |

| Status          | Out of production<br>(3 chambers world wide)  | Production<br>(many)                        |  |

| Chamber<br>view | O<br>Insulator<br>Cas Line<br>O<br>Gas Plate  | Chamber<br>Disultation<br>Disultation       |  |

| 비고              | Complex<br>43ea PM Parts<br>Total 150ea Parts | Simple<br>15ea PM Parts<br>Total 37ea Parts |  |

## WHEN will this change occur?

New process plan to be implement in Fab on W1945 Foundry plan to remove Old tool on W1950

Wafer Level Qualification:

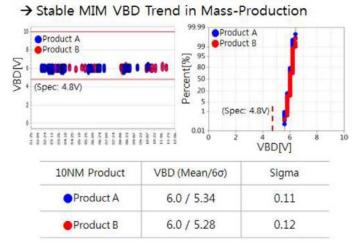

MIM capacitor with new process has been qualified through wafer level reliability test

- Extrinsic Breakdown (Vramp): No extrinsic breakdown found in other product Mass production

- 2) HAH MIM Vramp Data (@0.2V/0.03s, 25C)

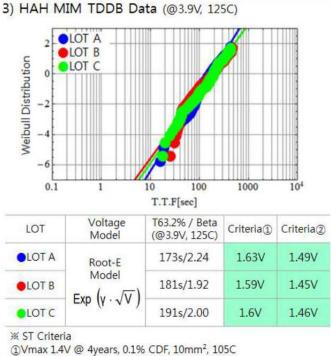

• Breakdown Life time Model (TDDB) on 3 lots: Passing Mission Profile criteria (Vmax > Vuse)

2Vmax 1.155V @10years, 0.1% CDF, 10mm<sup>2</sup>, 125C

See Appendices for Qualification plan. Estimate Date of Final Qualification: W1945

## **APPENDICES:**

APPENDIX 1 Qualification plan

**APPENDIX 1: QUALIFICATION PLAN**

## Reliability Qualification Plan: MIM module process change in Samsung Foundry: MIM HAH stack implementation on 32LP, 28LP and 28FD Technologies

| General Information              |                   | Lo                 | cations         |

|----------------------------------|-------------------|--------------------|-----------------|

| Silicon<br>process<br>technology | CMOS28nm LP       | Wafer fab location | Samsung Foundry |

| Affected products                | H310 (Cannes 2.0) |                    |                 |

## **Objectives:**

The objective of this qualification plan is to define the trials to validate the Metal Insulator Metal (MIM) capacitance insulator (dielectric) change from Ta2O5 material to HfO2/Al2O3/HfO2 (HAH) tri-layer for performance and throughput/capacity improvement at Samsung Foundry on 32LP, 28LP and 28FD Technologies

Estimate Date of Final Qualification: W1945

#### Description of the change:

| Process items                               | Current process | Current tool | New process                                                                           | New tool |

|---------------------------------------------|-----------------|--------------|---------------------------------------------------------------------------------------|----------|

| MIM Insulator<br>(dielectric)<br>Deposition | Ta₂O₅ layer     | Emeral3000   | HfO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub><br>(HAH) tri-layer | Pulsar   |

## Strategy for qualification:

Focus on two Test Vehicles products worst case in term of MIM area and MIM voltage Vuse.

| Product   | Comments                    |

|-----------|-----------------------------|

| Product A | MIM area: 3.77mm2 @ 1.0V    |

|           | MIM area: 19.92mm2 @ 1.1V   |

| Product B | MIM area: 52.5 mm2 @ 0.70 V |

| H310      | MIM area: 5.6 mm2 @ 1.0V    |

#### Lot definition and traceability:

| Lot<br>Nb | Product   | Si Foundry |

|-----------|-----------|------------|

| 1         | Product A | Samsung    |

| 2         | Product A | Samsung    |

| 3         | Product B | Samsung    |

## **Reliability Test Results:**

| Test      | Test short descr                     | iption                                |        |           |          |  |

|-----------|--------------------------------------|---------------------------------------|--------|-----------|----------|--|

|           | Method                               | Conditions                            | SS/Lot | Lot<br>n# | Duration |  |

| 3 IR      | Reflow simulation                    | (3 times) with standard JEDEC profile |        |           |          |  |

|           | JESD22-A113                          |                                       | 120    | 1         | NA       |  |

|           |                                      |                                       | 120    | 2         |          |  |

|           |                                      |                                       | 60     | 3         |          |  |

| 3 IR+TC   | Temperature cycling test             |                                       |        |           |          |  |

|           | JESD22-A104                          | Ta= -55/+125°C for Product A          | 30     | 1         | 1000 cy  |  |

|           |                                      | Ta= -40°C/125°C for Product B         | 30     | 2         |          |  |

|           |                                      | Steps: 0, 500, 1000 cycles            | 30     | 3         |          |  |

| 3 IR+HTOL | High Temperature Operating Life test |                                       |        |           |          |  |

|           | JESD22-A108                          | Vnom + 10%                            | 80     | 1         | 1000 hrs |  |

|           |                                      | Tj>135°C                              | 80     | 2         |          |  |

|           |                                      | Steps: 0, 500, 1000 hours             | 30     | 3         |          |  |

Comment about Lot 3: Due to high device costs and board availability, only 30 samples used for HTOL trial.

#### CONFIDENTIALITY OBLIGATIONS:

This document contains confidential information; its distribution is submitted to ST authorization.

Disclosure of this document to any non-authorized party must be previously authorized by ST only under the provision of a signed NDA between ST and Customer and must be treat as strictly confidential.

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

Information in this document is intended as support for authorized communication between ST and Customer only, for internal discussions purposes.

In no event the information disclosed by ST to Customer here under can be used against ST, or in a claim brought in front of any Court or Jurisdiction.

At all times you will comply with the following securities rules:

- $\cdot \operatorname{Do}$  not copy or reproduce all or part of this document

- Keep this document locked away

• Further copies can be provided on a "need to know basis", Please contact your local ST Sales Office or document writer

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a trademark of STMicroelectronics International NV and/or its affiliates, registered in the U.S. and other countries

© 2017 STMicroelectronics International NV and/or its affiliates – All Rights Reserved www.st.com